详解服务器内存和显存基础知识

作者 | Hardy

责编 | 阿秃

早期内存通过存储器总线和北桥相连,北桥通过前端总线与CPU通信。从Intel Nehalem起,北桥被集成到CPU内部,内存直接通过存储器总线和CPU相连。

所以,在AMD采用Socket FM1,Intel采用LGA 1156插槽之后的处理器都集成了北桥,独立的北桥已经消失,主板上仅余下南桥。

计算机体系的主要矛盾在于CPU太快了,而磁盘太慢了。所以它俩是不能够直接通信的,需要增加一个过渡层,这就是内存的作用。哈佛结构是一种将程序指令存储和数据存储分开的存储器结构。

内存(Memory)也被称为内存储器,其作用是用于暂时存放CPU中的运算数据,以及与硬盘等外部存储器交换的数据。计算机中所有程序的运行都是在内存中进行的,因此内存的性能对计算机的影响非常大。

1996年底,SDRAM开始在系统中出现,不同于早期的技术,SDRAM的出现是为了与CPU的计时同步化所设计。

SDRAM亦可称为SDR SDRAM(Single Data Rate SDRAM),Single Data Rate为单倍数据传输率,SDR SDRAM的核心、I/O、等效时脉皆相同, SDR SDRAM在1个周期内只能读写1次,若需要同时写入与读取,必须等到先前的指令执行完毕,才能接着存取。

DDR SDRAM为双通道同步动态随机存取内存,是新一代的SDRAM技术。别于SDR(Single Data Rate)单一周期内只能读写1次,DDR的双倍数据传输率指的就是单一周期内可读取或写入2次。在核心频率不变的情况下,传输效率为SDR SDRAM的2倍。

总结:

DDR采用时钟脉冲上升、下降沿各传一次数据,1个时钟信号可以传输2倍于SDRAM的数据,所以又称为双倍速率SDRAM。它的倍增系数就是2。

DDR2 SDRAM为双通道两次同步动态随机存取记忆体。DDR2内存Prefetch又再度提升至4bit(DDR的两倍),DDR2的I/O时脉是DDR的2倍。

总结:

DDR2仍然采用时钟脉冲上升、下降时各传一次数据的技术(不是传2次),但是一次预读4bit数据,是DDR一次预读2bit的2倍,因此,它的倍增系数是2X2=4。

DDR3SDRAM为双通道三次同步动态随机存取记忆体。DDR3记忆体Prefetch提升至8bit,即每次会存取8 bits为一组的数据。DDR3传输速率介于800~1600 MT/s之间。

此外,DDR3 的规格要求将电压控制在1.5V,较DDR2的1.8V更为省电。DDR3也新增ASR (Automatic Self-Refresh)、SRT(Self-Refresh Temperature)等两种功能,让内存在休眠时也能够随着温度变化去控制对内存颗粒的充电频率,确保系统数据完整性。

总结:

DDR3作为DDR2的升级版,最重要的改变是一次预读8bit,是DDR2的2倍,DDR的4倍,所以,它的倍增系数是2*2*2=8。

DDR4 SDRAM提供比DDR3/DDR2更低的供电电压1.2V以及更高的频宽。DDR4 新增了4 个Bank Group 组的设计,各个Bank Group具备独立启动操作读、写等动作特性,Bank Group 组可套用多工的观念来想像,亦可解释为DDR4 在同一时脉工作周期内,至多可以处理4 组数据,效率明显好过于DDR3。

另外,DDR4增加了DBI(Data BusInversion)、CRC(Cyclic Redundancy Check)、CA parity等功能,让DDR4内存在更快速与更省电的同时亦能够增强信号的完整性和储存的可靠性。

Intel在2017年推出对应于六代酷睿Skylake的服务器平台“Purley”,采用14nm工艺、最多28核心56线程、6通道DDR4内存、光纤互连通道,采用UPI总线替代QPI总线等等。UPI是 UltraPath Interconnect(超级通道互连)缩写,数据传输率可达9.6GT/s、10.4GT/s,带宽更足,灵活性更强,每条消息可以发送多个请求。

内存未来三大演进方向分别为容量、电压和频率。

-

容量越来越大(4GB -> 8GB -> 16GB ->32GB -> 64GB->…512GB)

-

电压越来越低(1.5v -> 1.35v -> 1.2v->…)

-

频率越来越高(1333 -> 1600 -> 1866-> 2133 -> 2400->..3200)

主流内存生产厂家分为内存颗粒厂商和模组厂商,三大内存颗粒(DRAM)原厂依次为Samsung、SK Hynix和Micron。模组厂商Ramaxel和Kingston通过从颗粒厂商购买颗粒制作内存条(DIMM)。

内存有三种不同的频率指标,它们分别是核心频率、时钟频率和有效数据传输频率。

-

核心频率即为内存Cell阵列(Memory Cell Array)的工作频率,它是内存的真实运行频率;

-

时钟频率即I/OBuffer(输入/输出缓存)的传输频率;

-

有效数据传输频率则是指数据传送的频率。

系统最大内存带宽 = 内存标称频率*内存总线位数*通道数*CPU个数

实际内存带宽 = 内存标称频率*内存总线位数*实际使用的通道数

实际内存带=内存核心频率*内存总线位数*实际使用的通道数*倍增系数。

从SDRAM-DDR时代,数据总线位宽时钟没有改变,都为64bit,但若是采用双通道技术,可以获得64*2=128bit的位宽。

下面计算一条标称DDR31066的内存条在默认频率下的带宽,1066是指有效数据传输频率,除以8才是核心频率,一条内存只用采用单通道模式,位宽为64bit。所以,实际内存带宽=(1066/8)*64*1*8=68224Mbit。

由此可知,如果内存工作在标称频率的时候,可以直接用标称频率*位宽*实际使用的通道数,简化公式=1066*64*1=68224Mbit。

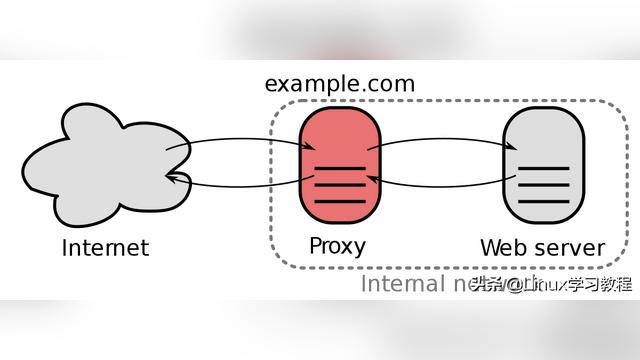

如果说内存带宽是处理器与内存交换数据的关键,那么显存带宽对显卡同样也很重要。GPU核心负责运算,显存负责数据存储,二者之间需要频繁交换数据,这就要依赖显存带宽了,更高的带宽可以让显卡在处理高分辨率、高画质时更加得心应手。

显存带宽从大的方面来说是显存频率及显存位宽来决定的,不过实际带宽就要看具体情况了,目前主流显卡的位宽多是128bit、256bit、384bit及512bit,更能决定带宽的还是显存类型,它们决定了显存带宽的极限。

目前最主流的显存当然是GDDR5,之前还有过昙花一现的GDDR4,现在低端市场上还有gDDR3显存残存,AMD在其显卡上使用了HBM显存,相比GDDR5显存更强大,带宽大幅提升。

就这二者来说,GDDR5内部I/O带宽是32bit,目前的NVIDIA显卡的GDDR5显存频率可以达到1750MHz,它是4倍速率机制,数据频率是7Gbps,单个芯片的带宽是28GB/s。目前的HBM显存的频率只有500MHz,2倍频率率机制,数据频率是1Gbps,不过它的I/O带宽极高,弥补了频率不足。

GDDR5和HBM显存是目前最主流的显存技术。目前gDDR3显存基本上是NVIDIA及AMD部分低端显卡在用。GDDR5绝对是目前的主流,单颗芯片的容量逐渐从之前的2Gb提高到4Gb,美光前不久还量产出货了8Gb(1GB)颗粒的,高端显卡也只要4-8颗芯片即可实现4-8GB容量显存,这将进一步推动大容量显卡的出现。

HBM是后起之秀,目前只有是AMD家独使用,第一代HBM技术其堆栈的显存核心容量2Gb(1个堆栈是4颗核心),数据频率1Gbps,位宽1024bit。

显存带宽=显存等效数据频率(Gbps)*显存总位宽(bit)/8=显存实际频率(MHz)*显存数据倍率(1、2、4不等)*显存等效位宽(64-512bit不等)/8

由于显卡厂更习惯用数字更大更好看的数据频率来标记产品规格,上述公司实际上还可以更简单,直接变成:

显存带宽(GB/s)=显存数据频率(Gbps)*显存等效位宽(bit)/8

拿NVIDIA的GeForce GT 720显卡来举例说明,该卡位宽仅为64bit,同时支持gDDR3和GDDR5显存,前者的典型频率900MHz,后者的典型频率是1250MHz,两种配置下带宽分别是:

gDDR3:

GT 720显卡的带宽为:900MHz *2*64 bit/8= 14.4GB/s,或者是1.8Gbps *64bit/ 8= 14.4GB/s。

GDDR5:

GT 720显卡的带宽为1250MHz *4*64 bit/8 = 40GB/s,或者是5Gbps* 64bit/8=40GB/s。