Chiplet生态之争

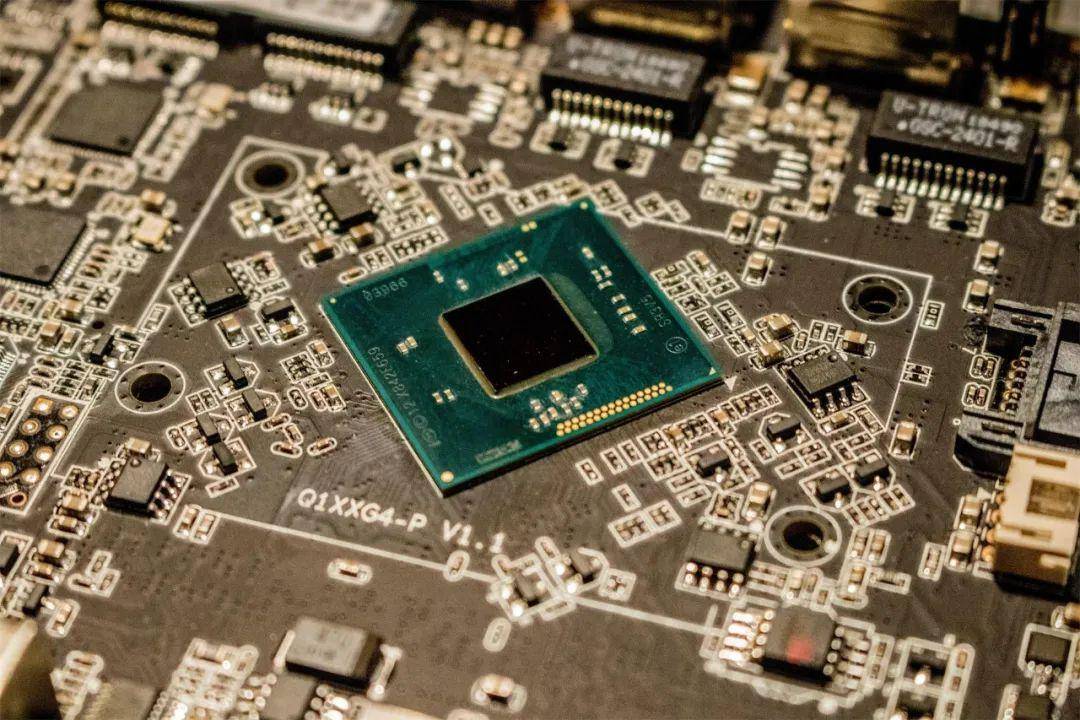

随着先进工艺逼近物理极限,高昂的研发费用和生产成本,导致芯片的性能提升无法持续等比例延续,先进封装以及Chiplet(芯粒)正在掀起后摩尔时代的新一轮半导体技术演进。英特尔、台积电等半导体龙头,日月光、长电科技、通富微电等封测大厂,都将Chiplet作为未来的主攻方向。

Chiplet的核心是实现芯片间的高速互联,将不同工艺、不同类型的芯片整合在一起,从而解决芯片设计中面临的复杂度大幅提升问题,以及先进制程中面临的高成本、低良率问题。这就使标准化工作在Chiplet发展中显得非常重要,因为只有将标准建立起来,才能让不同的芯粒之间真正实现互连互通。

事实上,很多公司此前都已推出基于自身的Chiplet产品。比如台积电开发的SoIC技术,可为用户提供类似于3D封装代工制造服务。英特尔开发的Foveros技术,可以将同为逻辑芯片的10nm处理器内核与22nm处理器内核以3D堆叠的方式封装在一起。其他Foundry和OSAT厂商也在推出各种先进封装工艺。

但是,这些芯片之间大部分都基于专有接口进行互连,不同厂家的Chiplet并不能进行通信和组合。而要扩大Chiplet的采用范围,就需要使用开放的接口标准进行互连,不同芯片之间才能相互通信。理论上统一了Chiplet接口标准,大家的芯粒都可以互连,这会让大量的芯片公司参与进来,做出各种功能的芯粒;芯片集成商则可以根据功能和应用需求,对芯粒进行自由组合,这将促进整个Chiplet生态的开放和繁荣。

去年3月,英特尔、AMD、ARM、微软、谷歌、台积电、三星、日月光等行业巨头成立通用芯粒互连(Universal Chiplet Interconnect Express,UCIe)产业联盟,使Chiplet的标准化有力地向前迈进了一步。

然而,去年公布的UCIe 1.0标准仍不完善。从UCIe联盟公布的白皮书来看,UCIe由三层协议构成,包括协议层、适配层和物理层。UCIe 1.0规范中选择了成熟的PCIe和CXL互连总线标准,主要是针对协议层,但要使Chiplet做到真正实现互联,不仅需要定义协议层,物理层的标准化同样重要,这涉及到不同厂商在晶圆制造、先进封装环节采用的技术工艺、技术路线,实现起来还需要一个过程,也需要相应标准的进一步推进与完善。

Chiplet技术的核心是生态之争,竞争的焦点是标准。目前,Chiplet最大的局限在于整个生态系统还没有建立完善,关键则要打通底层的技术标准。这些年随着Chiplet概念的持续发酵,许多公司都产生了很多好的想法,但由于生态圈不成熟,尚无法落地。目前能落地多为逻辑芯片与内存的堆叠互联,模拟芯片、MEMS、光电器件间的整合仍待探索。

不过,Chiplet从概念提出到产业推进,持续的时间还不久,很多技术标准需要完善,这也为中国企业切入Chiplet行业,并发挥更大作用,提供了空间。目前不仅有越来越多中国企业,如阿里巴巴、芯原股份、芯耀辉、芯动科技等,加入UCIe产业联盟,中国的Chiplet技术标准也被制订与发布出来。

去年12月,中国电子工业标准化技术协会发布国内首个《小芯片接口总线技术要求》团体标准(T/CESA 1248-2023),标准描述了CPU、GPU、人工智能芯片、网络处理器和网络交换芯片等应用场景的Chiplet技术要求。日前,中国Chiplet产业联盟也发布了《芯粒互联接口标准》,该标准为高速串口标准,基于国内封装及基板供应链进行优化。

从技术层面来看,国内企业在Chiplet上并不占优势。但中国是全球最大的电子信息产业制造基地,拥有广阔的下游市场,能定义的应用场景极为丰富。以此为基础,中国企业在Chiplet领域有着巨大的发展机会。而标准则是掌握住这个机会的关键一环。

封测三巨头押注Chiplet

Chiplet:在芯片“丛林”中披荆斩棘

作者丨 陈炳欣

编辑丨邱江勇

美编丨马利亚

监制丨 赵晨