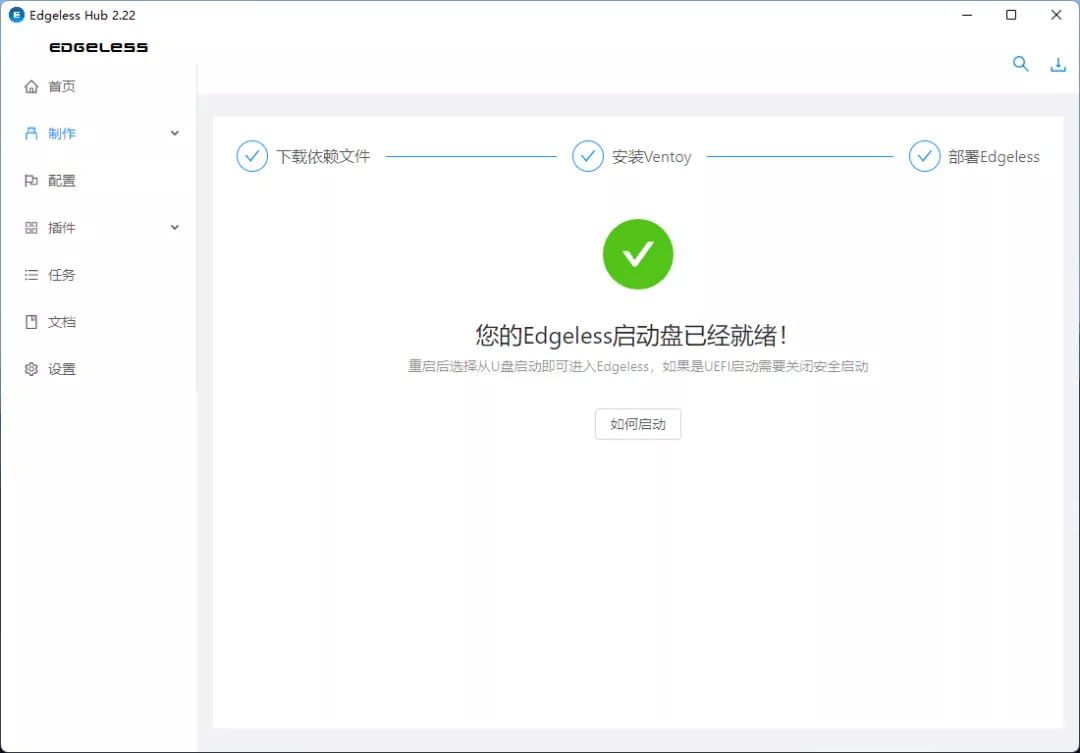

胶水多核等于Low?处理器封装没有那么简单!

昨天CFan报道了英特尔未来将推出十六核心的第十二代酷睿处理器的消息(详见《8+8+1架构见过没!英特尔第十二代酷睿竟抄袭ARM?》)。不过,不少小伙伴都担心这次又是“胶水”多核,而且一提到“胶水”就感觉非常Low。实际上,在当前的处理器市场,胶水已经泛滥,而且它也没有我们想象的那般不堪。

源于“胶水”的多核心

现在的我们都知道,在绝大多数情况下处理器的性能与核心数量成正比,多核“吊打”单核就是天经地义。

然而,如何在1颗芯片里塞进(通过封装技术)更多核心?这个问题曾一度困扰着整个半导体行业。

将时间的指针拨回到1995年Pentium Pro的诞生前夜,受当年落后制程工艺(350nm~500nm)的拖累,别说在1颗芯片内实现双核设计,就连高速二级缓存单元都无法同时与运算核心在1颗晶圆颗粒内共存。

因此,当时英特尔的解决思路是使用2颗晶圆颗粒,分别用于制造运算核心与高速二级缓存(L2),再将它们一起封装进1块CPU的基板上,最终造出了Pentium Pro。而这种将双晶圆“胶合”在一起设计,就是“胶水双核”概念的最早来源。

在未来的时间里,英特尔将“胶水”设计进一步发扬光大——先是将2个单核心整合封装的“奔腾D”(Pentium D)双核处理器,再到将2个双核心整合封装的Core 2 Quad四核处理器,“胶水”的工艺和配方不断成熟,这种“胶合”在一起的多核处理器的表现也有所改善。

当然,这种由胶水粘贴出来的多核处理器依旧饱受争议,在当年曾一度掀起了“真假双核”和“真假四核”的讨论,大体结论是“真多核”性能大多领先“假多核”,以至于一提到“胶水多核”大家就一脸鄙夷。

时至今日,类似的“胶水”技术仍在处理器领域混的风生水起,只是它已经不仅限于单纯CPU运算单元,而是可以“胶合”更多模块。

“胶水”技术再度兴盛

所谓的“胶水”,主要指的就是MCM (MCM-Multichip Module,多芯片模块)技术,它能将多颗芯片和其他单元组装在同一块多层互连基板上,然后进行封装,从而形成高密度和高可靠性的微电子组件。

第一代酷睿Westmere处理器,将CPU和GPU封装在同一块基板内,它们之间使用QPI总线相连

继Pentium Pro、Pentium D和Core 2 Quad之后,英特尔还利用MCM技术先后将CPU和GPU、CPU和PCH、CPU和eDRAM缓存打包组合。

自第二代酷睿起英特尔将内存控制器、PCI控制器、GPU全部整合进单CPU芯片后,从第四代移动版酷睿Haswell开始,英特尔又将PCH南桥芯片与CPU封装在同一块基板内

集成Iris核显的28W处理器,其中较小的芯片为eDRAM缓存

AMD也没闲着。

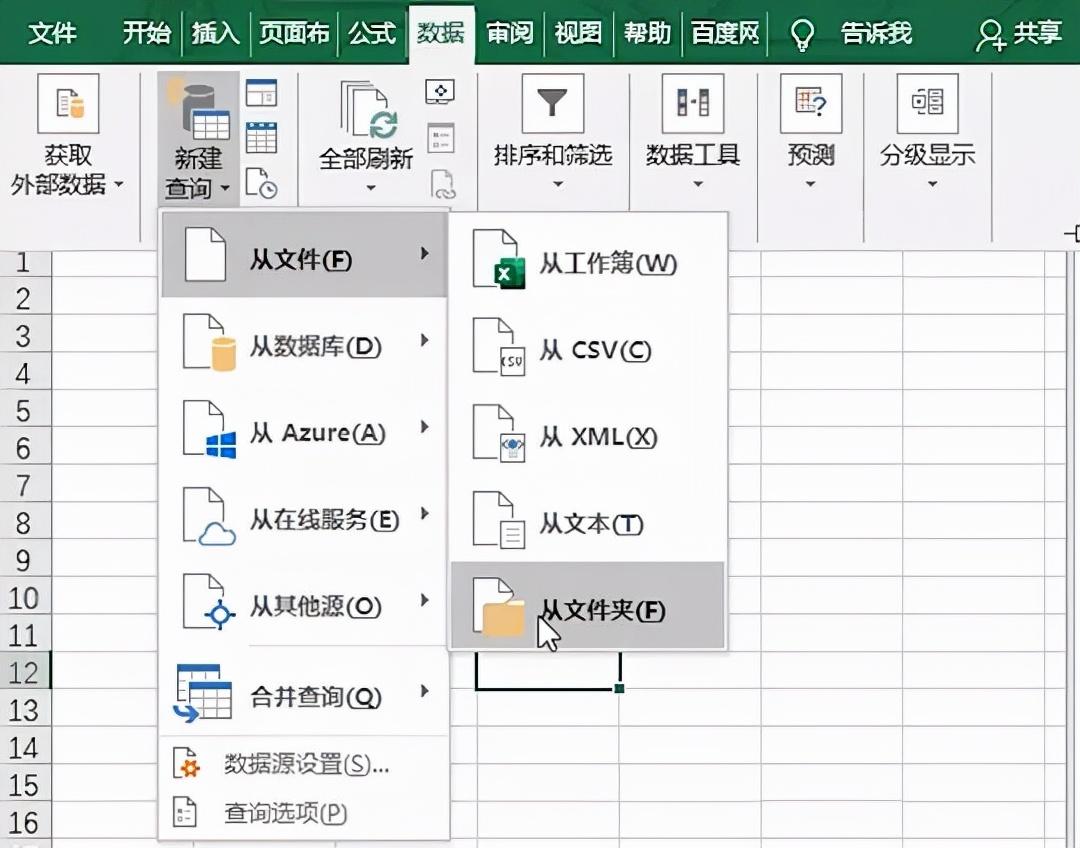

进入Zen架构时代之后,AMD在Ryzen锐龙及EPYC霄龙处理器上也引入了MCM技术(官方称为CCX多核架构),它们可以在一块基板上封装多个CPU Die,每个CPU Die都集成最多8核心16线程的CPU和32MB三级缓存等单元。

想拥有更多的物理核心和性能,只需搭配不同数量的CPU Die即可。

I/O die单元为14nm,CPU Die单元为10nm,同一基板上不同的Die由MCM技术胶合封装

类似的“胶水多核”还见于英特尔最新的Cascade Lake-AP 48核处理器,其本质是由两个24核的Cascade Lake处理器通过MCM技术组合而来,也并非原生48核。

虽然在历史上“胶水多核”的名声非常不好,但这项技术在今天却有着浴火重生的态势。究其原因,还是摩尔定律逐渐失效,提升频率和增加核心之路变得越发艰难。

理论上讲,将CPU、GPU、缓存、I/O等控制器打包到同一块晶圆芯片上(单片电路)最是完美,但在半导体工艺逐渐逼近物理极限的情况下,既想要更多核心,还要更高主频,集成包括CPU、PCH、I/O单元、DDR内存控制器、PCIe控制器和IF控制器在内的所有常见功能模块,成本还不能太高——纯属做梦!

因此。在现有工艺的水平上,最经济可行的解决方案,唯有异构MCM之路。

然而,处理器基板的面积有限,表面多颗芯片之间的通讯还存在延迟的隐患,这就需要处理器厂商优化封装技术,并引入更高速的总线接口。

封装技术的立体演进

想将不同功能模块单元胶合在同一块基板上看起来很容易,但现实情况却是困难重重。

比如,不是所有功能模块都需要最先进的工艺,CPU和GPU用7nm,内存控制器14nm就足够了,想将这些不同工艺的芯片融合在一起,还要降低成本和保证良品率,这可不是传统2D封装技术能搞定的,于是就有了2.5D封装技术。

在2.5D封装技术上,知名的方案主要以台积电的“InFO”(整合型扇出)和英特尔“EMIB”(嵌入式多芯片互连桥接)为主,前者能以较低成本的有机封装来链接芯片,但在密度上不如EMIB。

此外。AMD曾在Fury X显卡首次商业化的HBM显存技术、新一代锐龙处理器7nm CPU Die和14nm I/O Die单元分离的设计,也是利用了2.5D封装将GPU核心与HBM核心整合在一个底座上。

我们可以将以英特尔EMIB为代表的2.5D封装技术理解为“平面版”的乐高积木,可以在一个固定大小的平面上,横向固定不同样式和大小的积木块。

在处理器领域,这些积木块就变成了由不同工艺打造的不同功能模块,比如将7nm工艺的CPU、10nm的GPU、14nm的I/O单元、22nm的通讯单元等等。

EMIB的意义就在于能将不同制程的芯片组合在同一基板的封装之中,同时它还具有正常的封装良品率、不需要额外的工艺、设计简单等优点。

英特尔和AMD携手打造的“Kaby Lake-G”平台处理器(整合CoffeeLake-H架构的CPU、AMD Vega架构的GPU以及4GB HBM2显存)以及Stratix 10 FPGA就是EMIB技术的首次预演。

问题来了,2.5D封装技术可以容纳多少功能模块取决于基板大小,对于绝大多数处理器的芯片尺寸而言,空间总是不够用的。

此时,就需要一种类似“立体版”的乐高积木了,可以像盖楼一般将所有需要的功能模块一层层地纵向叠加累积起来。

引领未来的3D封装技术

提起芯片的堆叠,可能很多朋友都会想到智能手机——几乎所有的新款手机都会选择将内存芯片覆盖在处理器芯片上以节省主板空间,叠放还能让处理器和内存间的引线长度最短,从而降低线路噪音、访问延迟、电力损耗。手机领域的这种内存和处理器“叠罗汉”的设计即PoP(元件堆叠装配),它并非3D封装,而是“堆叠”,属于一种多成品芯片之间的焊接技术。

真正的“3D封装”,应该是一种晶圆对晶圆(Wafer-On-Wafer)无凸起的键合(Bonding)3D IC制程技术。目前符合这一标准的技术,主要以台积电旗下的“SoIC”,以及英特尔主推的“Foveros”的3D封装技术为主。

先来看看台积电的SoIC技术,它是基于CoWoS与多晶圆堆叠技术开发的新一代创新封装技术,利用硅穿孔(TSV)技术将多种不同性质的临近芯片整合在一起,用于结合的机密材料(号称价值十亿美元)能直接透过微小的孔隙沟通多层的芯片,在减少厚度的同时还能增加多倍以上的性能。

英特尔的Foveros技术的原理是通过TSV和微凸块(Micro-Bumps)技术,堆叠其他的晶圆芯片和微芯片。

它可以让只能在EMIB封装技术中以平面分布的功能模块纵向立体的摞在一起,在牺牲一点点厚度的前提下就可进一步压缩处理器基板的尺寸。

以英特尔Lakefield处理器为例,它在12mm×12mm的面积里就集成了1个10nm制程的Sunny Cove架构CPU大核、4个10nm制程的Tremont架构CPU小核、以及LPDDR4内存控制器、L2和L3缓存以及Gen11 GPU单元。

Lakefield处理器和主板与签字笔的大小对比

作为目前最高级的“胶水”,3D封装技术能在更小尺寸的芯片里就整合更多的功能模块。

然而,在制程工艺已逼近物理极限,异构计算大行其道,更多不同类型的芯片需要被集成在一起的大环境下,无论SoIC还是Foveros似乎都还有所不足。

为了实现基于封装技术,就能在更小尺寸的基板上打造出集成多类型小芯片的SoC系统级单芯片的梦想,英特尔祭出了“终极胶水”——将2.5D封装EMIB和3D封装Foveros技术优势集于一身的“Co-EMIB”方案,它能在将多芯片横向拼接的同时,还能在任意芯片的表面继续叠高楼,并通过全方位互连(ODI)技术、裸片间接口(MDIO)技术和硅通孔(TSV)技术解决多芯片矩阵之间互联通讯和延迟等问题。

值得一提的是,AMD在推出HBM显存产品,实现了GPU芯片和显存芯片的2.5D整合封装后,也即将跟进3D封装技术,初级目标是将DRAM/SRAM和处理器(CPU/GPU)通过TSV(硅穿孔)的方式整合在一颗芯片中,虽然形式上与手机领域的PoP封装处理器+内存颗粒相似,但底层技术却更加先进。

总之,在异构计算时代,“胶水多核”已经不再是招人嘲笑的对象,而是一种符合历史发展潮流的必然选择。只是,借助封装技术将更多芯片灵活的“打包”后,需要面临更为严苛的散热问题,开发人员需要更加精心地考虑系统的结构(甚至影响系统的物理结构和芯片的核心架构),以适应、调整各个热点。