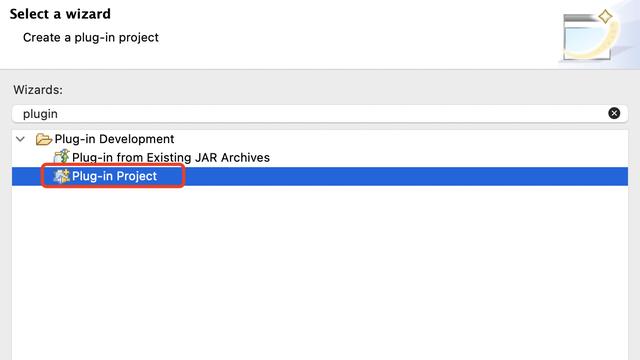

硬核知识——聊聊CPU缓存和缓存一致性

左图为最简单的高速缓存的配置,数据的读取和存储都经过高速缓存,CPU核心与高速缓存有一条特殊的快速通道;主存与高速缓存都连在系统总线上(BUS)这条总线还用于其他组件的通信

在高速缓存出现后不久,系统变得越来越复杂,高速缓存与主存之间的速度差异被拉大,直到加入了另一级缓存,新加入的这级缓存比第一缓存更大,并且更慢,而且经济上不合适,所以有了二级缓存,甚至是三级缓存

1.为什么需要CPU cache?

CPU的频率太快了,快到主存跟不上,这样在处理器时钟周期内,CPU常常需要等待主存,浪费资源。 所以cache的出现,是为了缓解CPU和内存之间速度的不匹配问题(结构:cpu->cache->memory)。

2.CPU cache 存在的原理?

局部性原理:CPU 访问存储器时,无论是存取指令还是存取数据,所访问的存取单元都趋于聚集在一个较小的连续区域中。

时间局部性:如果某个数据被访问,那么在不久的将来他很可能被再次访问。

空间局部性:如果某个数据被访问,那么与他相邻的数据很快也可能被访问。

3.缓存一致性(MESI)

MESI协议中cache line数据状态有4种,引起数据状态转换的CPU cache操作也有4种,因此要理解MESI协议,就要将这16种状态转换的情况讨论清楚。

初始场景:在最初的时候,所有的CPU中都没有数据,其中一个CPU发生读操作,此时发生RR(数据从主内存中读取到当前CPU的cache),状态为E(独占,只有当前CPU有数据,并且和主存一致)。此时,如果有其他CPU也读取主存数据,则状态修改为S(共享,多个CPU之间拥有相同数据,并且和主存保持一致),如果其中一个CPU发生数据修改,那么该CPU中数据状态修改为M(拥有最新数据,和主存不一致,但是以当前CPU中的数据为准),并通知其他拥有该数据的CPU数据失效,其他CPU中的cache line状态修改为I(失效,和主存中的数据被认为不一致,数据不可用应该重新获取)

modify

场景:当前CPU中数据状态是modify,表示当前CPU中拥有最新数据,虽然主存中的数据和当前CPU中的数据不一致,但是以当前CPU中的数据为准;

- LR:此时如果发生local read,即当前CPU读数据,直接从cache中获取数据,拥有最新数据,因此状态不变;

- LW:直接修改本地cache数据,修改后也是当前CPU拥有最新数据,因此状态不变;

- RR:因为本地内存中有最新数据,因此当前CPU不会发生RR和RW,当本地cache控制器监听到总线上有RR发生的时,必然是其他CPU发生了读主存的操作,此时为了保证一致性, 当前CPU应该将数据写回主存,而随后的RR将会使得其他CPU和当前CPU拥有共同的数据,因此状态修改为S;

- RW(将当前CPU缓存中的数据写入到主内存里面):同RR,当cache控制器监听到总线发生RW,当前CPU会将数据写回主存,因为随后的RW将会导致主存的数据修改,因此状态修改成I;

exclusive

场景:当前CPU中的数据状态是exclusive,表示当前CPU独占数据(其他CPU没有数据),并且和主存的数据一致;

- LR:从本地cache中直接获取数据,状态不变;

- LW:修改本地cache中的数据,状态修改成M(因为其他CPU中并没有该数据,因此不存在共享问题,不需要通知其他CPU修改cache line的状态为I);

- RR:因为本地cache中有最新数据,因此当前CPU cache操作不会发生RR和RW,当cache控制器监听到总线上发生RR的时候,必然是其他CPU发生了读取主存的操作,而RR操作不会导致数据修改,因此两个CPU中的数据和主存中的数据一致,此时cache line状态修改为S;

- RW:同RR,当cache控制器监听到总线发生RW,发生其他CPU将最新数据写回到主存,此时为了保证缓存一致性,当前CPU的数据状态修改为I;

shared

场景:当前CPU中的数据状态是shared,表示当前CPU和其他CPU共享数据,且数据在多个CPU之间一致、多个CPU之间的数据和主存一致;

- LR:直接从cache中读取数据,状态不变;

- LW:发生本地写,并不会将数据立即写回主存,而是在稍后的一个时间再写回主存,因此为了保证缓存一致性,当前CPU的cache line状态修改为M,并通知其他拥有该数据的CPU该数据失效,其他CPU将cache line状态修改为I;

- RR:状态不变,因为多个CPU中的数据和主存一致;

- RW:当监听到总线发生了RW,意味着其他CPU发生了写主存操作,此时本地cache中的数据既不是最新数据,和主存也不再一致,因此当前CPU的cache line状态修改为I;

invalid

场景:当前CPU中的数据状态是invalid,表示当前CPU中是脏数据,不可用,其他CPU可能有数据、也可能没有数据;

- LR:因为当前CPU的cache line数据不可用,因此会发生RR操作,此时的情形如下。

A. 如果其他CPU中无数据则状态修改为E;

B. 如果其他CPU中有数据且状态为S或E则状态修改为S;

C. 如果其他CPU中有数据且状态为M,那么其他CPU首先发生RW将M状态的数据写回主存并修改状态为S,随后当前CPU读取主存数据,也将状态修改为S;

- LW:因为当前CPU的cache line数据无效,因此发生LW会直接操作本地cache,此时的情形如下。

A. 如果其他CPU中无数据,则将本地cache line的状态修改为M;

B. 如果其他CPU中有数据且状态为S或E,则修改本地cache,通知其他CPU将数据修改为I,当前CPU中的cache line状态修改为M;

C. 如果其他CPU中有数据且状态为M,则其他CPU首先将数据写回主存,并将状态修改为I,当前CPU中的cache line状态修改为M;

- RR:监听到总线发生RR操作,表示有其他CPU读取内存,和本地cache无关,状态不变;

- RW:监听到总线发生RW操作,表示有其他CPU写主存,和本地cache无关,状态不变;

总结

MESI协议为了保证多个CPU cache中共享数据的一致性,定义了cache line的四种状态,而CPU对cache的4种操作可能会产生不一致状态,因此cache控制器监听到本地操作和远程操作的时候, 需要对地址一致的cache line状态做出一定的修改,从而保证数据在多个cache之间流转的一致性。

作者:habit_learning

链接:https://www.jianshu.com/p/893f25eac96f

来源:简书

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。