一文读懂:到底什么是Chiplets?

50多年来,Intel和AMD一直是两家主流的处理器公司。

虽然两者都使用x86 ISA来设计新品,但是在过去十多年左右的时间里,两家cpu公司却走上了完全不同的道路。

大约在2000年代中期,随着推土机(Bulldozer)芯片推出,AMD在与Intel的竞争中节节败退。低IPC和低效的设计组合几乎让AMD公司进入绝境。

这种槽糕的表现持续了近十年,直到2017年,随着AMD Zen微架构的到来,情况开始发生变化。

新的Ryzen处理器标志着AMD对cpu设计方法的彻底的重构,将重点放在了IPC、单线程性能上面。最值得注意的是,AMD转向MCM或Chiplets设计。而在那时候,Intel仍在做着与2011年Sandy Bridge问世以来几乎一模一样的事情。

▉ 一切都始于Zen

在发布Zen架构的时候,AMD通过提供比酷睿i5-7600K等部件更多的内核和线程来搅局Intel中端产品。

但是由于在延迟等方面的问题,以及Ryzen缺乏针对游戏的优化, Intel在游戏等方面依然占据着显著的性能领先地位。但Zen架构的成功推出,还是给AMD打了一针强心剂,在性能、功耗及规格方面终于有了与英特尔同一水平的产品,终于可以让AMD稍微喘口气了。

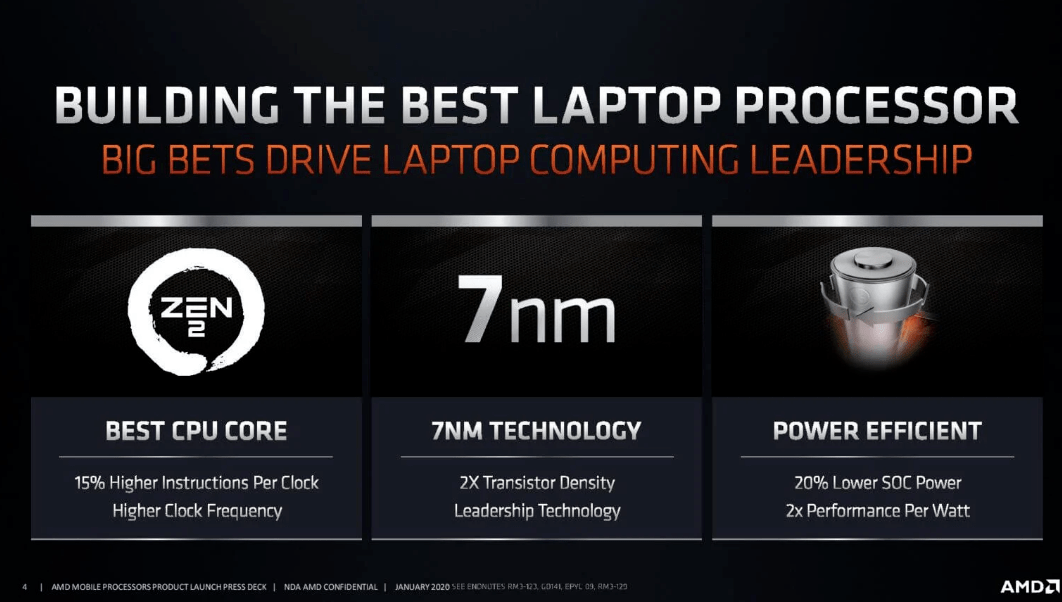

随着基于Zen 2的Ryzen 3000 cpu的推出,AMD的游戏部分开始有所改善,而英特尔的游戏王冠最终被随着基于Zen 3的Ryzen 5000 cpu的发布被抢走。对IPC的巨大改进意味着AMD能够提供更多的内核,而且在单线程工作负载上也能与Intel匹敌。

AMD能够在Zen 2的时候大获成功,与其大胆的尝试有很大关系。

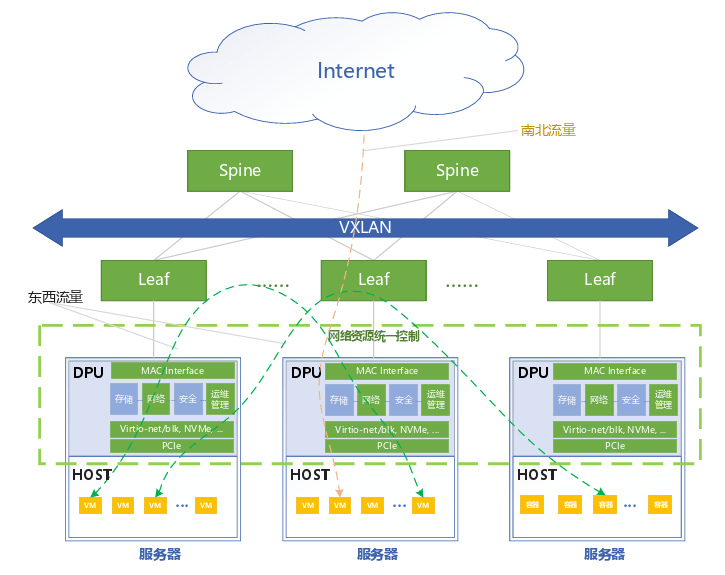

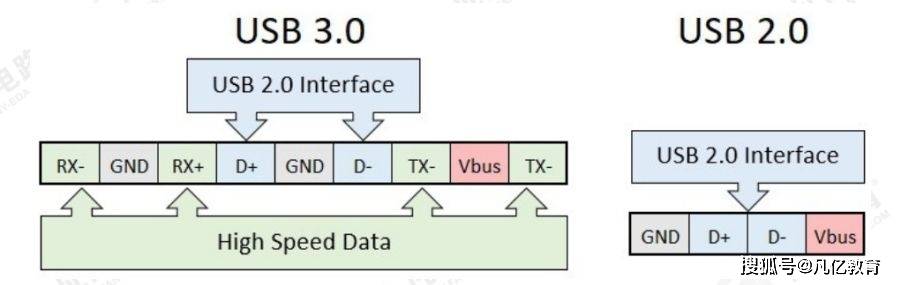

AMD放弃了过去CPU里尽可能集成多功能的做法,将计算核心和I/O接口部分分离,进行了更灵活的调配,也就是我们所说的Chiplets小芯片技术。

Chiplets设计不同于以往的胶水封装,本质上是把不同工艺、不同架构的芯片电路按需搭配,比单纯的胶水封装要高明,也要复杂。

为了方便更好的理解Chiplets,我们将CPU比喻成一个西瓜。为了满足用户越来越高的需求,传统的方式是通过方法让西瓜长的越来越大。但当西瓜足够大的时候,你很难再让西瓜继续长大,同时还增加了西瓜可能坏掉的风险。Chiplets的方式则是提供两个、四个小西瓜来满足用户的对越来越大的需求。

一个不够,多个来凑的做法虽然看起来很简单,但是在处理架构设计上却是一个非常难得的创新。

AMD在Zen2上采用这样的设计无疑是很聪明的做法,配置也非常灵活,提升CPU核心数量就堆CPU模块即可,所以锐龙处理器可以从之前的8核16线程轻松变成16核32线程。

此外,AMD这样做也需要生产小核心,提高了良率,降低了成本,而且IO核心使用的还是更成熟的14nm工艺,进一步削减了成本。

▉ 单片设计vs Chiplets设计

在当时,Intel采用的单片处理器设计方法。从本质上讲,这意味着需要将内核、缓存和I/O资源等都要放在同一个单片芯片上。

这种方法有一些明显的优点就是降低了延迟。由于所有的模块都在同一个基板上,所以不同的内核通信、访问缓存和访问系统内存所需的时间要少得多。延迟减少,这将带来最佳性能。

如果其他条件都相同,那么单片方法将始终为您带来最佳性能。不过,这有一个很大的缺点。这是在成本和扩展方面。

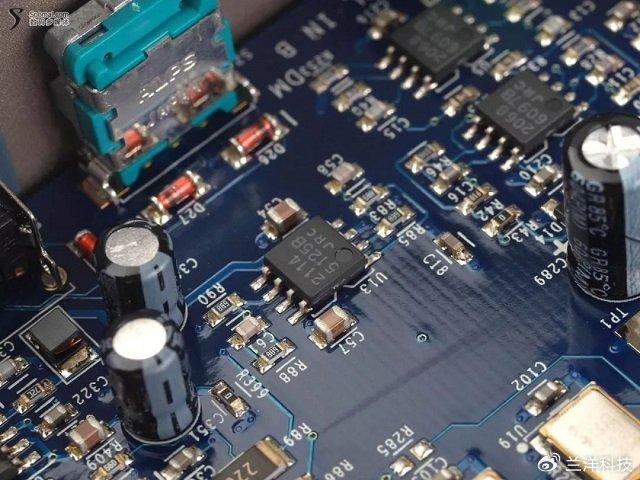

当代工厂生产cpu(或任何硅片)时,他们几乎无法实现100%的良品率的产量。

如果你采用成熟的工艺节点,比如英特尔的14nm+++,你的良品率将超过70%。这意味着您将获得大量可用的cpu。然而,反过来说,每生产10个cpu,就必须丢弃至少2-3个有缺陷的单元。被丢弃的单位显然是要花钱制造的,所以成本必须考虑到最终的销售价格。

在低核数的情况下,单一的方法可以很好地工作。这在很大程度上解释了为什么英特尔的主流消费级CPU产品线之前一直都只有4核。但是,当您增加核心数量时,单一方法会导致指数级的成本增加。

为什么会这样呢?

在整体式芯片上,每个内核都必须具有功能。如果您要制造八核芯片,而八核中的七核可以工作,那么您仍然不能使用它。还记得我们所说的超过90%的收益率吗?从数学上讲,单片芯片上每增加一个内核就有10%的缺陷率叠加,以至于使用20核Xeon,英特尔实际上必须为每一个可用芯片丢掉一两个缺陷芯片,因为所有20个内核必须起作用。成本不仅随核心数量线性增长,而且由于浪费而成倍增长。

此外,当扩大14nm产能时,新工厂的处理器产量将无法达到现有工厂的水平。这已经导致Intel的处理器短缺。

所有这一切的结果是,Intel的工艺在低核数下具有价格和性能竞争力,但在高核数下就站不住脚了,除非他们降低销售利润或者亏损。对于Intel来说,制造双核和四核处理器比AMD交付Ryzen 3 sku要便宜得多。

接下来我们要讲下为什么会这样。

▉ Chiplets有何优势?

AMD采用基于芯片或MCM(多芯片模块)的方法来设计处理器。把每个Ryzen CPU看作是多个独立的处理器,用AMD的话说就是用超级胶水粘在一起。

一个Ryzen CCX具有4核/8核处理器,以及L3缓存。两个CCX(带有Zen 3的单个8核CCX)被粘在CCD上以创建一个芯片,这是基于Zen的Ryzen和Epyc cpu的基本构建块。多达8个ccd可以堆叠在单个MCM(多芯片模块)上,允许消费级Ryzen处理器(如Threadripper 3990X)最多64核。

这种方法有两大优势。第一个优势是,成本或多或少与核心数量呈线性关系。由于AMD的浪费率与其相对于最多能够创建功能性4核模块(单个CCX)有关,因此他们不必丢弃大量有缺陷的CPU。第二个优势来自于它们能够利用那些有缺陷的CPU本身的能力。英特尔只是将它们淘汰了,而AMD则逐个CCX禁用了功能内核,以实现不同的内核数量。

例如,Ryzen 7 5800X和5600X都有一个8核的CCD。后者禁用了两个核心,使其具有6个功能核心,而不是8个。当然,这使得它能够以比英特尔更有竞争力的价格销售六核部件。

但是,什么事情都有两面性,Chiplets方法有一个很大的缺点:延迟。每个晶片都在单独的物理基板上。由于物理定律,这意味着Ryzen cpu在Infinity Fabric上的通信会产生延迟惩罚。这在第一代Ryzen上最为明显。因此,Infinity Fabric速度与内存时钟和内存超频相关,因此可以显著提高CPU性能。

AMD设法通过Ryzen 3000 cpu纠正了这一点,然后通过新推出的Ryzen 5000系列进一步改进了这一点。前者引入了一个大型L3缓存缓冲区,称为"游戏缓存"。L3缓存是系统内存和低级CPU核心缓存(L1和L2)之间的中介。通常情况下,消费级处理器的L3空间很小,例如英特尔的i7 9700K就只有12 MB的L3空间。然而,AMD为3700X配备了32mb的L3内存,而3900X配备了64mb的L3内存。

L3缓存均匀分布在不同的核之间。增加的缓存量意味着,通过一些智能调度,内核可以缓存更多它们需要的东西。缓冲区消除了Infinity Fabric带来的大部分延迟损失。

Ryzen 5000 cpu更进一步,取消了四个核心CCX,取而代之的是八个核心综合体,每个核心直接连接到CCX/CCD上的其他核心。这改善了核间延迟、缓存延迟和带宽,并为每个核提供了两倍的L3缓存,显著提高了游戏性能。

▉ Chiplets,未来潮流?

作为后摩尔时代最关键的技术之一,Chiplets将满足特定功能的裸片通过die-to-die内部互联技术,多个模块芯片与底层基础芯片的系统封装,实现新形式IP复用。在当前技术进展下,Chiplets方案可实现芯片设计复杂度及设计成本降低,且有利于后续产品迭代,加速产品上市周期。

在如此明显的优势之下,Chiplets自然得到了众多国际巨头的青睐。作为AMD的老对手,Intel也在2023年发布了基于Chiplets技术的第四代至强可扩展处理器和至强CPU Max,以及数据中心GPU Max。

据了解,至强CPU Max拥有56个性能核,内核的4个小芯片使用EMIB连接,进行自然语言处理时高带宽内存优势可提升20倍性能。而数据中心GPU Max是英特尔针对高性能计算加速设计的第一款GPU产品,一个封装中有超过1000亿个晶体管,拥有47个不同的块和高达128GB的内存。

在未来的几年中,我们更可能会看到更多Chiplets方法的使用。这是因为摩尔定律(要求每两年将处理能力提高一倍)已经全面放慢了,单个处理器内核的速度不会每两年提高一倍。

因此,提高性能的唯一方法就是扩展内核和堆叠内核,才让近年来硬件圈仍能保持较快的发展速度。未来对Chiplets的研究,也将继续推进下去。